# AN438

### Philips Semiconductors Application Note EIE/AN90015

### Summary

This application note presents a set of software routines to drive the  $I^2C$  interface in 8xC528 type of microcontrollers. A description of the  $I^2C$  interface is given. Examples show how to use these routines in PL/M-51, C and assembly source code.

### **1.0 INTRODUCTION**

This application note describes the  $l^2C$  interface of the 8xC528 microcontroller and gives a set of routines in application programs to drive this interface.

Chapter 2.0 gives a hardware description of the bit level I<sup>2</sup>C. It gives an overview of what functions are done in hardware by the interface and the functions that should be implemented by software. The registers described are accessible with software and control the I<sup>2</sup>C interface.

Chapter 3.0 gives a description of the routines that may be used by the application program. The routines are written in such a way that the  $I^2C$  interface becomes transparent to the user. the slave program is described in more detail, because this routine may be adapted by the user for his specific application.

Chapter 4.0 gives simple example programs that show how to use the routines in assemble, PL/M and C application programs.

#### References:

| <ul> <li>The I<sup>2</sup>C-bus specification</li> </ul>          | 9398 358 10011     |

|-------------------------------------------------------------------|--------------------|

| - 80C51-based 8-bit Microcontrollers                              | Data handbook IC20 |

| <ul> <li>PLM51 I<sup>2</sup>C Software Interface IIC51</li> </ul> | ETV/AN89004        |

### 2.0 THE I<sup>2</sup>C INTERFACE

### 2.1 Characteristics of I<sup>2</sup>C Interface

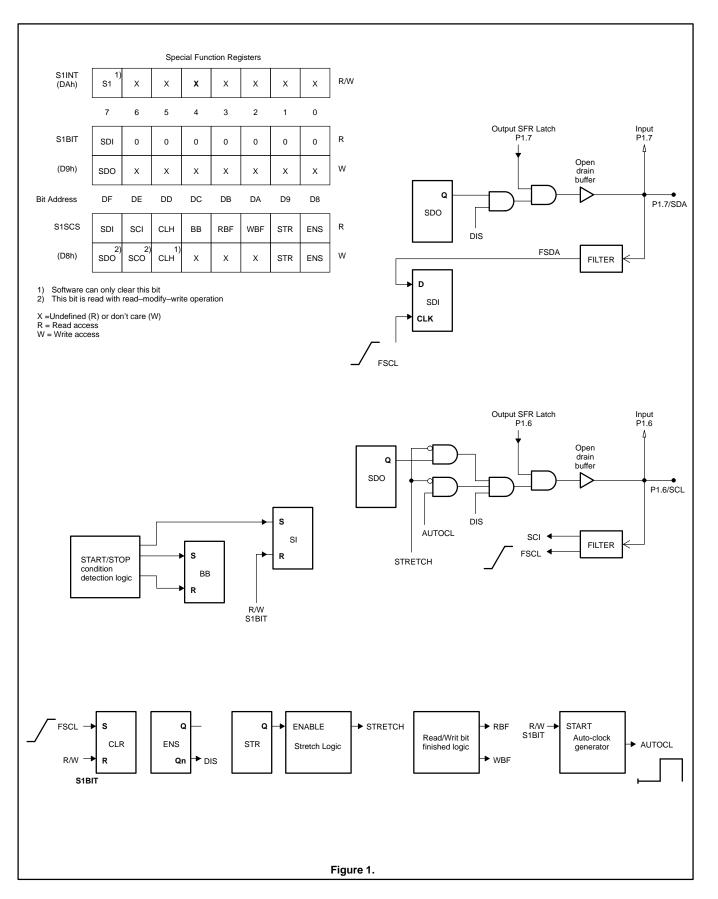

The Block diagram of the bit-level I<sup>2</sup>C interface is shown on page 2. P1.6/SCL and P1.7/SDA are the serial I/O pins. These two pins meet the I<sup>2</sup>C specification concerning the input levels and output drive capability. Consequently, these pins have an open drain configuration. All four modes of the I<sup>2</sup>C bus can be used:

- Master transmitter

- Master receiver

- Slave transmitter

- Slave receiver

The advantages of using the bit-level  $I^2C$  hardware compared with a full software implementation are:

- Higher bit rate

- No critical software timing requirements

- Less software overhead

- More reliable data transfer

The bit-level I<sup>2</sup>C hardware can perform the following functions:

- Filtering the incoming serial data and clock signals. Glitches shorter than 4 XTAL periods are rejected.

- Recognition of a START or STOP condition.

- Generating an interrupt request after reception of a START condition.

- Setting the Bus Busy flag when a START condition is detected.

- Clearing the Bus Busy flag when a STOP condition is detected.

- Recognition of a serial clock pulse on the SCL line.

- Latching the serial data bit on the SDA line at every rising edge on the SCL line.

- Stretching the LOW period of the serial clock SCL to synchronizer with external master devices.

- Setting the Read Bit Finished (RBF) or Write Bit Finished (WBF) flag is an error free bit transfer has occurred.

- Setting a Clock LOW-to-HIGH (CLH) flag when a leading edge is detected on the SCL line.

- Generation of serial clock pulse on SCL in master mode.

The following functions must be done with software:

- Handling the I<sup>2</sup>C interrupt caused by a detected START condition.

- Conversion of serial to parallel data when receiving.

- Conversion of parallel to serial data when transmitting.

- Comparing received slave address with own slave address.

- Interpretation of acknowledge information.

- Guarding the I^2C status if the RBF and WBF flags indicate a not regular bit transfer.

- Generating START/STOP conditions when in master mode.

- Handling bus arbitration when in master mode.

### Application note

# I<sup>2</sup>C routines for 8XC528

AN438

### 2.2 Control and Status Registers

Control of the I<sup>2</sup>C bus hardware is done via 3 Special Function Registers:

#### S1INT

This register contains the serial interrupt flag SI.

#### S1BIT

For read, this register contains the received bit SDI. For write, this register contains bit SDO to be transmitted.

### S1SCS

For read, this register contains status information. For write, this register is used as control register.

#### S1INT: I<sup>2</sup>C Interrupt Register 2.2.1

S1INT.7 is the Serial Interrupt request flag (SI).

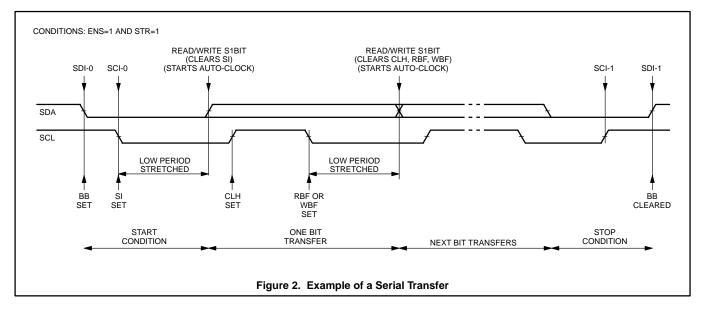

If the serial I/O is enabled (ENS = 1), then a START condition will be detected and the SI flag is set on the falling edge of the filtered SCL signal.

Provided that EA (global enable) and ES1 (enable I<sup>2</sup>C interrupt) are set (in the interrupt enable IE register), SI generates an interrupt that will start the slave address receive routine.

SI is cleared by accessing the S1BIT register or by writing '00H' to S1INT. SI cannot be set by software.

After reception of a START condition, the LOW period of the SCL pulse is stretched, suspending serial transfer to allow the software to take appropriate action. This clock stretching is ended by accessing the S1BIT register.

#### S1BIT: Single Bit Data Register 2.2.2

S1BIT.7 contains two physical latches: the Serial Data Output (SDO) latch for a write operation, and the filtered Serial Data Input (SDI) latch for a read operation. SDI data is latched on the rising edge of the filtered SCL pulse. S1BIT.7 accesses the same physical latches as S1SCS.7, but S1BIT.7 is not bit addressable.

Reading or writing S1BIT register starts the next additional actions:

- SI, CLH, RBF and WBF flags are cleared.

- Stretching the LOW period of the SCL clock is finished.

- Auto-clock pulse is started if enabled.

The auto-lock is an active HIGH SCL pulse that starts 28 Xtal periods after an access to S1BIT. SCL remains high for 100 Xtal periods. If the SCL line is kept LOW by any device that wants to hold up the bus transfer, the auto-clock counter still runs for 20 Xtal periods to try to make SCL high and then go into a wait-state. This will result in a minimum SCL HIGH time of 80 Xtal periods  $(5\mu s \text{ at } f_{Xtal} = 16 \text{ MHz}).$

The auto-clock signal will be inhibited if the SCO flag in the S1SCS register is set to '1'. SCL pulses must then be generated by software. In this situation, access to S1BIT may be used to clear the SI, CLH, RBF and WBF flags.

A quick check on a successful bit transfer from/to SDO/SDI is carried out be testing only the RBF or WBF flag (see 2.2.3).

#### 2.2.3 S1SCS: Control and Status Register

S1SCS.7 represents two physical latches, the Serial Data Output (SDO) latch for write operations and the Serial Data Input (SDI) latch for read operations. S1SCS.7 accesses the same physical latches as S1BIT.7, but S1SCS.7 is bit addressable. However, a

read or write operation of S1SCS.7 does not start an auto-lock pulse, with not finish clock stretching, and will not clear flags.

S1SCS.6 represents two physical latches, the Serial Clock Output (SCO) latch for write operations and the Serial Clock Input (SCI) latch for read operations. The output of SCO is "OR-ed" with the auto-clock pulse. If SCO = '1' the auto-clock generation is disabled and its output is LOW. Internal clock stretching logic and external devices can then pull the SCL line LOW.

If the auto-clock is not used, the SCL line has to be controlled by setting SCO = '1', waiting for CLH to become '1' and setting SCO = '0' after the specified SCL HIGH time. Data access should be done via S1SCS.7.

- S1SCS.5 is the serial Clock LOW-to-HIGH transition flag (CLH). This flag is set by a rising edge of the filtered serial clock. CLH = '1' indicates that no devices are stretching SCL LOW, and since the last CLH reset, a new valid data bit has been latched in SDI.

CLH can be cleared by writing '0' to S1SCS.5 or by a read or write operation to the S1BIT register. Clearing CLH also clears RBF and WBF. Writing a '1' to S1SCS.5 will not affect CLH.

- S1SCS.4 is the Bus Busy flag (BB). BB is set or cleared by hardware only. If set, it indicates that a START condition has been detected on the I<sup>2</sup>C bus. A STOP condition clears the BB flag.

- S1SCS.3 is the Read Bit Finished flag (RBF). If RBF = 1, it indicates that a serial bit has been received and latched into SDI successfully. If during a bit transfer RBF is '0', the cause is indicated as follows:

| SCI = '1' |                                               |

|-----------|-----------------------------------------------|

| and       |                                               |

| CLH = '1' | The SCL pulse is not finished and still HIGH. |

|           | A bus device is deleving the transfer by      |

| CLH = '0' | A bus device is delaying the transfer by stretching the LOW level on the SCL line.       |

|-----------|------------------------------------------------------------------------------------------|

| BB = '0'  | A STOP-condition has been detected during the bit transfer. This should be considered as |

SI = '1' A START-condition has been detected during the bit transfer. This should be considered as a bus-error.

RBF can be cleared by clearing CLH or by a read or write operation to the S1BIT register.

a bus-error.

- S1SCS.2 is the Write Bit Finished flag (WBF). If set, it indicates that a serial bit in SDO has been transmitted successfully. If during bit transfer WBF is '0', the following conditions may be the cause:

| SCI = '1'<br>and<br>CI H = '1' | The SCL pulse is not finished and still UICH                                                           |

|--------------------------------|--------------------------------------------------------------------------------------------------------|

|                                | The SCL pulse is not finished and still HIGH.                                                          |

| CLH = '0'                      | A bus device is delaying the transfer by<br>stretching the LOW level on the SCL line.                  |

| BB = '0'                       | A STOP-condition has been detected during the bit transfer. This should be considered as a bus-error.  |

| SI = '1'                       | A START-condition has been detected during the bit transfer. This should be considered as a bus-error. |

WBF can be cleared by clearing CLH or access to the S1BIT register.

S1SCS.1 is the STRetch control flag (STR). STR can be set or cleared by software only. Setting STR enables the stretching of SCL LOW periods. Stretching will occur after a falling edge on the filtered serial clock. This allows synchronization with the SCL clock signal of an external master device.

If STR is cleared, no stretching of the SCL LOW period will occur after the transfer of a serial bit.

The LOW level on the SCL line is also stretched after a START condition is received, regardless of the STR contents. The stretching of the SCL LOW period is finished by a read or write operation of the S1BIT register.

- S1SCS.0 is the ENable Serial I/O flag (ENS).

ENS can be set or cleared by software only.

ENS = '0' disables the serial I/O. The I/O signals P1.6/SCL and P1.7/SDA are determined by the port latches of P1.6 and P1.7 (open drain). If P1.6 and P1.7 are connected to an I<sup>2</sup>C bus, then the flags SDI, SCI, CLH, and BB still monitor the I<sup>2</sup>C bus status, but will not influence the I/O lines, nor will they request an interrupt.

ENS = '1' enables the START detection and clock stretching logic. Note that the P1.6 and P1.7 latches and the SDO and SCO control flags must be set to '1' before ENS is set to avoid SCL and/or SDA to pull the lines LOW.

### 3.0 I<sup>2</sup>C ROUTINES

### 3.1 Introduction

A set of routines is written for the I<sup>2</sup>C interface that supports multi-master and slave operation. The routines are placed in a library I2C\_DR.LIB. If I2C\_DR.LIB is linked to an application program, only the needed object modules are linked in the output file.

The routines can be used as device driver for PL/M-51, C and 8051-assembly code. By using these routines the bit-level  $I^2C$  interface is fully transparent for the user.

The routines use the following 8xC528 resources:

- Exclusive use of Register\_Bank\_1. Only R7 of this register bank contains static data (Own Slave Address). R0..R6 may be used by the application program when the I<sup>2</sup>C routine is finished.

- 7 bytes DATA used for parameter passing.

- 1 byte Bit-Addressable DATA for status flags.

When using routines from this library DPH, DPL, PSW (except CY) and B are not altered.

An n-bytes data buffer is used as destination or source buffer for the bytes to be received/transmitted and reside in DATA or IDATA memory space.

The code is written to generate the highest transfer rate on the  $I^2C$  bus. At  $f_{Xtal} = 16MHz$  this will result in a bit rate of 87.5kbit/sec.

The following software tools from BSO/Tasking are used for program development:

- OM4142 Cross Assembler 8051 for DOS: V3.0b

- OM4144 PL/M 8051 Compiler for DOS: V3.0a

- OM4136 C8051 Compiler for DOS: V1.1a

- OM4129 XRAY51 debugger: V1.4c

#### 3.2 Functional Description

When using these routines in a PL/M application program, they must be declared EXTERNAL. In this declaration the user can specify the type returned by each procedure. All procedures (except Init\_IIC and Dis\_IIC) can return a BIT or BYTE, depending on the chosen EXTERNAL declaration. The BIT or BYTE returned is '0' if the I<sup>2</sup>C was successful. If a BYTE is returned, the following check bits are available for the user:

| BYTE.0 | An I <sup>2</sup> C error has been detected.                                       |

|--------|------------------------------------------------------------------------------------|

| BYTE.1 | No ACK received.                                                                   |

| BYTE.2 | Arbitration lost.                                                                  |

| BYTE.3 | Time out error. This may be caused by an<br>external device pulling SCL LOW.       |

| BYTE.4 | A bus error has occurred. This may be a spurious START/STOP during a bit transfer. |

| BYTE.5 | No access to I <sup>2</sup> C bus.                                                 |

| BYTE.6 | 0                                                                                  |

| BYTE.7 | 0                                                                                  |

|        |                                                                                    |

Note that typed procedures must be called using an expression. If the result of an  $I^2C$  procedure is to be ignored, a dummy assignment must be done for a typed procedure. The examples in the following section assume that the procedures are called from a PL/M program. Examples will be given later how to use these routines with C and assembly application programs.

#### 3.2.1 Init\_IIC

#### Declaration

#### Init\_IIC:

PROCEDURE (Own\_Slave\_Address, Slave\_Sub\_Address) EXTERNAL;

DECLARE (Own\_Slave\_Address, Slave\_Sub\_Address) BYTE; END;

#### Description

Init\_IIC must be called after RESET, before any procedure is called. The I<sup>2</sup>C interface and I<sup>2</sup>C interrupt will be enabled. The global enable interrupt flag, however, will not be affected. This should be done afterwards. Own\_Slave\_Address is passed to Init\_IIC for use as slave. Slave\_Sub\_Address is the pointer to a DATA buffer that is used for data transfer in slave mode. When used as master in a single master system, these parameters are not used.

#### Example

CALL Init\_IIC (54h,.Slave\_Data\_Buffer); ENABLE; /\* Enable Interrupts; EA=1 \*/

3.2.2 Dis\_IIC

#### Declaration

Dis\_IIC: PROCEDURE EXTERNAL;

#### Description

Dis\_IIC will disable the I<sup>2</sup>C-interface and the I<sup>2</sup>C-interrupt. The I<sup>2</sup>C interface will still monitor the bus, but will not influence the SDA and SCL lines.

### Example

CALL Dis\_IIC;

#### 3.2.3 IIC\_Test\_Device

#### Declaration

IIC\_Test\_Device: PROCEDURE (Slave\_Address) [BIT|BYTE] EXTERNAL; DECLARE (Slave\_Address) BYTE; END;

#### Description

IIC\_Test\_Device just sends the slave address to the  $l^2C$  bus. It can be used to check the presence of a device on the  $l^2C$  bus.

#### I<sup>2</sup>C Protocol

| S-SlvW-A-P | : Device is present, IIC_Error=0     |

|------------|--------------------------------------|

| S-SIvW-N-P | : Device is not present, IIC_Error=1 |

#### Example

DECLARE IIC\_Error BIT;

.....

$\label{eq:lic_error} \ensuremath{\mathsf{IIC\_Error=IIC\_Test\_Device(8Ch)}};$

IF (IIC\_Error) THEN

"Device not acknowledging on slave address" ELSE

"Device acknowledges on slave address"

## AN438

#### 3.2.4 IIC\_Write

#### Declaration

IIC\_Write:

PROCEDURE (Slave\_Address, Count, Source\_Ptr) [BIT|BYTE] EXTERNAL; DECLARE (Slave\_Address, Count, Source\_Ptr) BYTE; END;

#### Description

IIC\_Write is the most basic procedure to write a message to a slave device.

#### I<sup>2</sup>C Protocol

| L        | =Count              |

|----------|---------------------|

| D1[0L–1] | BASED by Source_Ptr |

S-SIvW-A-D1[0]-A....A-D1[L-1]-A-P

#### Example

DECLARE Data\_Buffer(4) BYTE;

CALL IIC\_Write(02Ch, LENGTH(Data\_Buffer),.Data\_Buffer);

#### 3.2.5 IIC\_Write\_Sub

#### Declaration

#### IIC\_Write\_Sub:

PROCEDURE (Slave\_Address, Count, Source\_Ptr, Sub\_Address) [BIT|BYTE] EXTERNAL; DECLARE (Slave\_Address, Count, Source\_Ptr, Sub\_Address) BYTE; END;

#### Description

IIC\_Write\_Sub writes a message preceded by a sub-address to a slave device.

#### I<sup>2</sup>C Protocol

| L        | =Count              |

|----------|---------------------|

| Sub      | =Sub_Address        |

| D1[0L-1] | BASED by Source_Ptr |

S-SlvW-A-Sub-A-D1[0]-A-D1[1]-A....A-D1[L-1]-A-P

#### Example

DECLARE Data Buffer(8) BYTE;

CALL IIC\_Write\_Sub (48h,LENGTH(Data\_Buffer),.Data\_Buffer,2);

#### IIC\_Write\_Sub\_SWInc 3.2.6

#### Declaration

#### IIC\_Write\_Sub\_SWInc:

PROCEDURE (Slave\_Address, Count, Source\_Ptr, Sub\_Address) [BIT|BYTE] EXTERNAL;

DECLARE (Slave\_Address, Count, Source\_Ptr, Sub\_Address) BYTE;

#### END; Description

Some I<sup>2</sup>C devices addressed with a sub-address do not automatically increment the sub-address after reception of each byte. IIC\_Write\_Sub\_SWInc can be used for such devices the same way as IIC\_Write\_Sub is used. IIC\_Write\_Sub\_SWInc splits up the message in smaller messages and increments the sub-address itself.

#### I<sup>2</sup>C Protocol

| L        | =Count              |

|----------|---------------------|

| Sub      | =Sub_Address        |

| D1[0L–1] | BASED by Source_Ptr |

S-SlvW-A- (Sub+0) - A-D1[0] - A-P S-SlvW-A- (Sub+1) - A-D1[1] - A-P

S-SlvW-A- (Sub+L-1)-A-D1[L-1]-A-P

#### Example

DECLARE Data\_Buffer(6) BYTE;

CALL IIC\_Write\_Sub\_SWInc(80h,LENGTH (Data\_Buffer),.Data\_Buffer,2);

#### IIC\_Write\_Memory 3.2.7

#### Declaration

#### IIC\_Write\_Memory:

PROCEDURE (Slave\_Address, Count, Source\_Ptr, Sub Address) [BIT|BYTE] EXTERNAL;

- DECLARE (Slave\_Address, Count, Source\_Ptr, Sub\_Address) BYTE;

- END;

### Description

I<sup>2</sup>C Non-Volatile Memory devices (such as PCF8582) need an additional delay after writing a byte to it. IIC\_Write\_Memory can be used to write to such devices the same way IIC\_Write\_Sub is used. IIC\_Write\_Memory splits up the message in smaller messages and increments the sub-address itself. After transmission of each message a delay of 40 milliseconds (f<sub>Xtal</sub> = 16 MHz) is inserted.

#### I<sup>2</sup>C Protocol

l

| L        | =Count              |

|----------|---------------------|

| Sub      | =Sub_Address        |

| D1[0L–1] | BASED by Source_Ptr |

S-SlvW-A- (Sub+0) - A-D1[0] - A-P Delay 40ms

S-SlvW-A- (Sub+1) - A-D1[1] - A-P Delay 40ms

S-SlvW-A- (Sub+L-1)-A-D1[L-1]-A-P Delay 40ms

#### Example

DECLARE Data\_Buffer(10) BYTE;

CALL IIC\_Write\_Memory(0A0h,LENGTH (Data\_Buffer),.Data\_Buffer,0F0h);

# I<sup>2</sup>C routines for 8XC528

#### 3.2.8 IIC\_Write\_Sub\_Write

#### Declaration

#### IIC\_Write\_Sub\_Write:

PROCEDURE (Slave\_Address, Count1, Source\_Ptr1, Sub\_Address, Count2, Source\_Ptr2) [BIT]BYTE] EXTERNAL; DECLARE (Slave\_Address, Count1, Source\_Ptr1, Sub\_Address, Count2, Source\_Ptr2) BYTE; END;

### Description

IIC\_Write\_Sub\_Write writes 2 data blocks preceded by a sub-address in one message to a slave device. This procedure can be used for devices that need an extended addressing method, without the need to put all data into one large buffer. Such a device is the ECCT (I<sup>2</sup>C controlled teletext device; see example).

#### I<sup>2</sup>C Protocol

| L        | =Count1              |

|----------|----------------------|

| M        | =Count2              |

| Sub      | =Sub_Address         |

| D1[0L–1] | BASED by Source_Ptr1 |

| D2[0M-1] | BASED by Source_Ptr2 |

S-SlvW-A-Sub-A-D1[0]-A-D1[1]-A-.... -A-D1[L-1]-A-D2[0]-A-D2[1]-A-....

-A-D2[M-1]-A-P

#### Example

PROCEDURE Write\_CCT\_Memory (Chapter, Row, Column, Data\_Buf, Data\_Count); DECLARE (Chapter, Row, Column, Data\_Buf, Data\_Count) BYTE;

/\*

The extended address (CCT-Cursor) is formed by Chapter, Row and Column. These three bytes are written after the sub-address (=8) followed by the actual data that will be stored relative to the extended address.

#### \*/

CALL IIC\_Write\_Sub\_Write (22h, 3, .Chapter, 8, Data\_Buf, Data\_Count); END Write\_CCT\_Memory;

#### 3.2.9 IIC\_Write\_Sub\_Read

#### Declaration

IIC\_Write\_Sub\_Read: PROCEDURE (Slave\_Address, Count1, Source\_Ptr1, Sub\_Address, Count2, Dest\_Ptr2) [BIT]BYTE] EXTERNAL; DECLARE (Slave\_Address, Count1, Source\_Ptr1, Sub\_Address, Count2, Dest\_Ptr2) BYTE; END;

### Description

IIC\_Write\_Sub\_Read writes a data block preceded by a sub-address, generates an  $I^2C$  restart condition, and reads a data block. This procedure can be used for devices that need an extended addressing method. Such a device is the ECCT.

### I<sup>2</sup>C Protocol

| L        | =Count1              |

|----------|----------------------|

| Μ        | =Count2              |

| Sub      | =Sub_Address         |

| D1[0L–1] | BASED by Source_Ptr1 |

| D2[0M-1] | BASED by Source_Ptr2 |

S-SlvW-A-Sub-A-D1[0]-A-D1[1]-A-.... -A-D1[L-1]-A-S-SlvR-A-D2[0]-A-D2[1]-A-.... -A-D2[M-1]-N-P

#### Example

PROCEDURE Read\_CCT\_Memory (Chapter, Row, Column, Data\_Buf, Data\_Count); DECLARE (Chapter, Row, Column, Data\_Buf, Data\_Count) BYTE;

/\*

The extended address (CCT-Cursor) is formed by Chapter, Row and Column. These three bytes are written after the sub-address (8). After that the actual data will be read relative to the extended address.

#### \*/

CALL IIC\_Write\_Sub\_Write (22h, 3, .Chapter, 8, Data\_Buf, Data\_Count); END Read\_CCT\_Memory;

# I<sup>2</sup>C routines for 8XC528

#### 3.2.10 IIC\_Write\_Com\_Write

#### Declaration

IIC\_Write\_Com\_Write:

PROCEDURE (Slave\_Address, Count1, Source\_Ptr1, Count2, Source\_Ptr2) [BIT|BYTE] EXTERNAL;

DECLARE (Slave\_Address, Count1, Source\_Ptr1, Count2, Source\_Ptr2) BYTE;

END;

#### Description

IIC\_Write\_Com\_Write writes two data blocks from different data buffers in one message to a slave receiver. This procedure can be used for devices where the message consists of 2 different data blocks. Such devices are, for instance, LCD-drivers, where the first part of the message consists of addressing and control information, and the second part is the data string to be displayed.

#### I<sup>2</sup>C Protocol

| L        | =Count1              |

|----------|----------------------|

| Μ        | =Count2              |

| D1[0L–1] | BASED by Source_Ptr1 |

| D2[0M–1] | BASED by Source_Ptr2 |

S-SlvW-A-D1[0]-A-D1[1]-A-.... -A-D1[L-1]-A-D2[0]-A-D2[1]-A-.... -A-D2[M-1]-A-P

#### Example

DECLARE Control\_Buffer(2) BYTE; DECLARE Data\_Buffer(20) BYTE;

.....

CALL IIC\_Write\_Com\_Write(74h, LENGTH(Control\_Buffer), .Control\_Buffer, LENGTH(Data\_Buffer), .Data\_Buffer);

#### 3.2.11 IIC\_Write\_Rep\_Write

#### Declaration

IIC\_Write\_Rep\_Write:

PROCEDURE (Slave\_Address1, Count1, Source\_Ptr1, Slave\_Address2, Count2, Source\_Ptr2) [BIT|BYTE] EXTERNAL; DECLARE (Slave\_Address1, Count1, Source\_Ptr1, Slave\_Address2, Count2, Source\_Ptr2) BYTE;

END;

#### Description

Two data strings are sent to separate slave devices, separated with a repeat START condition. This has the advantage that the bus does not have to be released with a STOP condition before the transfer from the second slave.

#### I<sup>2</sup>C Protocol

| L        | =Count1              |

|----------|----------------------|

| M        | =Count2              |

| SlvW1    | =Slave_Address1      |

| SlvW2    | =Slave_Address2      |

| D1[0L–1] | BASED by Source_Ptr1 |

| D2[0M-1] | BASED by Source_Ptr2 |

S-SlvW-A-D1[0]-A-D1[1]-....

```

-A-D1[L-1]-A-S-SlvW-A-D2[0]-A-D2[1]-....

-A-D2[M-1]-A-P

```

#### Example

DECLARE Data\_Buffer\_1(10) BYTE; DECLARE Data\_Buffer\_2(4) BYTE;

CALL IIC\_Write\_Rep\_Write (48h, LENGTH(Data\_Buffer\_1), .Data\_Buffer\_1, 50h, LENGTH(Data\_Buffer\_2), .Data\_Buffer\_2);

## AN438

#### 3.2.12 IIC\_Write\_Rep\_Read

#### Declaration

IIC\_Write\_Rep\_Read:

PROCEDURE (Slave\_Address1, Count1, Source\_Ptr1, Slave\_Address2, Count2, Dest\_Ptr2) [BIT|BYTE] EXTERNAL; DECLARE (Slave\_Address1, Count1, Source\_Ptr1, Slave\_Address2, Count2, Dest\_Ptr2) BYTE;

FND.

#### Description

A data string is sent and received to/from two separate slave devices, separated with a repeat START condition. This has the advantage that the bus does not have to be released with a STOP condition before the transfer from the second slave.

#### I<sup>2</sup>C Protocol

| L        | =Count1              |

|----------|----------------------|

| M        | =Count2              |

| SlvW1    | =Slave_Address1      |

| SlvW2    | =Slave_Address2      |

| D1[0L–1] | BASED by Source_Ptr1 |

| D2[0M-1] | BASED by Dest_Ptr2   |

#### S-SlvW-A-D1[0]-A-D1[1]-.... -A-D1[L-1]-A-S-SlvR-A-D2[0]-A-D2[1]-....

-A-D2[M-1]-N-P

### Example

DECLARE Data\_Buffer\_1(10) BYTE; DECLARE Data\_Buffer\_2(4) BYTE;

....

CALL IIC\_Write\_Rep\_Read (48h, LENGTH(Data\_Buffer\_1),

.Data\_Buffer\_1, 57h, LENGTH(Data\_Buffer\_2), .Data\_Buffer\_2);

### 3.2.13 IIC\_Read

### Declaration

IIC\_Read:

PROCEDURE (Slave\_Address, Count, Dest\_Ptr) [BIT|BYTE] EXTERNAL; DECLARE (Slave\_Address, Count, Dest\_Ptr) BYTE; END;

#### Description

IIC\_Read is the most basic procedure to read a message from a slave device.

#### I<sup>2</sup>C Protocol M

M =Count D2[0..M–1] BASED by Dest\_Ptr

S-SlvR-A-D2[0]-A-D2[1]-A.....A-D2[M-1]-N-P

#### Example

DECLARE Data\_Buffer(4) BYTE;

CALL IIC\_Read (0B5, LENGTH(Data\_Buffer), .Data\_Buffer);

#### 3.2.14 IIC\_Read\_Status

#### Declaration

IIC\_Read\_Status: PROCEDURE (Slave\_Address, Dest\_Ptr) [BIT|BYTE] EXTERNAL; DECLARE (Slave\_Address, Dest\_Ptr) BYTE; END;

#### Description

Several I<sup>2</sup>C devices can send a one byte status-word via the bus. IIC\_Read\_Status can be used for this purpose. IIC\_Read\_Status works the same way as IIC\_Read but the user does not have to pass a count parameter.

### I<sup>2</sup>C Protocol

Status BASED by Dest\_Ptr

S-SlvR-A-Status-N-P

#### Example

DECLARE Status\_Byte BYTE;

CALL IIC\_Read\_Status (84h, .Status\_Byte);

#### 3.2.15 IIC\_Read\_Sub

#### Declaration

IIC\_Read\_Sub: PROCEDURE (Slave\_Address, Count, Dest\_Ptr, Sub\_Address) [BIT|BYTE] EXTERNAL; DECLARE (Slave\_Address, Count, Dest\_Ptr, Sub\_Address) BYTE; END:

#### Description

IIC\_Read\_Sub reads a message from a slave device, preceded by a write of the sub-address. Between writing the sub-address and reading the message, an I<sup>2</sup>C restart condition is generated without releasing the bus. This prevents other masters from accessing the slave device in between and overwriting the sub-address.

### I<sup>2</sup>C Protocol

M =Count Sub =Sub\_Address D2[0..M-1] BASED by Dest\_Ptr

S-SlvW-A-Sub-A-S-SlvR-D2[0]-A-D2[1]-A.....A-D2[M-1]-N-P

### Example

DECLARE Data\_Buffer(5) BYTE;

CALL IIC\_Read\_Sub (0A3h, LENGTH(Data\_Buffer), .Data\_Buffer, 2);

# I<sup>2</sup>C routines for 8XC528

#### 3.2.16 IIC\_Read\_Rep\_Read

#### Declaration

IIC\_Read\_Rep\_Read:

PROCEDURE (Slave\_Address1, Count1, Dest\_Ptr1, Slave\_Address2, Count2, Dest\_Ptr2) [BIT|BYTE] EXTERNAL; DECLARE (Slave\_Address1, Count1, Dest\_Ptr1, Slave\_Address2, Count2, Dest\_Ptr2) BYTE;

END;

#### Description

Two data strings are read from separate slave device, separated with a repeat START condition. This has the advantage that the bus does not have to be released with a STOP condition before the transfer from the second slave.

#### I<sup>2</sup>C Protocol

| L        | =Count1            |

|----------|--------------------|

| M        | =Count2            |

| SlvW1    | =Slave_Address1    |

| SlvW2    | =Slave_Address2    |

| D1[0L–1] | BASED by Dest_Ptr1 |

| D2[0M-1] | BASED by Dest_Ptr2 |

S-SlvR-A-D1[0]-A-D1[1]-..... -A-D1[L-1]-N-S-SlvR-A-D2[0]-A-D2[1]-..... -A-D2[M-1]-N-P

#### Example

DECLARE Data\_Buffer\_1(10) BYTE; DECLARE Data\_Buffer\_2(4) BYTE;

•••••

CALL IIC\_Read\_Rep\_Read (49h, LENGTH(Data\_Buffer\_1), .Data\_Buffer\_1, 51h,

LENGTH(Data\_Buffer\_2), .Data\_Buffer\_2);

#### 3.2.17 IIC\_Read\_Rep\_Write

#### Declaration

IIC\_Read\_Rep\_Write: PROCEDURE (Slave\_Address1, Count1, Dest\_Ptr1, Slave\_Address2, Count2, Source\_Ptr2) [BIT|BYTE] EXTERNAL; DECLARE (Slave\_Address1, Count1, Dest\_Ptr1, Slave\_Address2, Count2, Source\_Ptr2) BYTE; END;

#### Description

A data string is received and sent from/to two separate slave devices, separated with a repeat START condition. This has the advantage that the bus does not have to be released with a STOP condition before the transfer from the second slave.

#### I<sup>2</sup>C Protocol

| L        | =Count1              |

|----------|----------------------|

| Μ        | =Count2              |

| SlvW1    | =Slave_Address1      |

| SlvW2    | =Slave_Address2      |

| D1[0L–1] | BASED by Dest_Ptr1   |

| D2[0M-1] | BASED by Source_Ptr2 |

S-SlvR-A-D1[0]-A-D1[1]-..... -A-D1[L-1]-N-S-SlvW-A-D2[0]-A-D2[1]-..... -A-D2[M-1]-A-P

#### Example

DECLARE Data\_Buffer\_1(10) BYTE; DECLARE Data\_Buffer\_2(4) BYTE;

CALL IIC\_Read\_Rep\_Write(49h, LENGTH(Data\_Buffer\_1), .Data\_Buffer\_1, 58h, LENGTH(Data\_Buffer\_2), .Data\_Buffer\_2);

#### 3.2.18 Slave Mode Routines

There are two ways for the I<sup>2</sup>C interface to enter the slave-mode:

- After an I<sup>2</sup>C interrupt the software must enter the slave-receiver mode to receive the slave address. This address will then be compared with its own address. If there is a match either slave-transmitter or slave-receiver mode will be entered. If no match occurs, the interrupted program will be continued.

- During transmission of a slave-address in master-mode, arbitration is lost to another master. The interface must then switch to slave-receiver mode to check if this other master wants to address the 8xC528 interface.

The slave-mode protocol is very application dependent. In this note the basic slave-receive and slave-transmit routines are given and should be considered as examples. The user may for instance send NO\_ACK after receiving a number of bytes to signal to the master-transmitter that a data buffer is full. A description of the code will be given later.

Slave parameters are given with the Init\_IIC procedure. The passed parameters are the own-slave-address and a source/destination-pointer to a data buffer.

The slave-routine will be suspended at the following conditions:

- Interrupts with higher priority. Slave-routine will be resumed again after interrupt is handled.

- If a NO\_ACKNOWLEDGE is received form a master-receiver.

- If a STOP condition is detected from a master transmitter.

Constraints for user software.

- The user must control the global enable (EA) bit.

- The user must control the priority level of the I<sup>2</sup>C interrupt. If the slave routine is interrupted by a higher priority interrupt, the SCL line will be stretched to postpone bus transfer until the higher interrupt is finished.

#### 3.3 The Slave Routine: SLAVE.ASM

The listing of the slave routine can be seen on page 12. The routine is written in such a way that stretching of SCL is minimized. Application code can be inserted in this routine and this will increase stretching time.

The routine has 2 entry points.

Entry via MST\_ENTRY happens when an arbitration error has occurred when transmitting a slave address in master mode.

Auto-clock generation will be disabled and SCL stretching enabled. The byte will be continued to be received and can later be compared with the own slave address.

The second entry point is via an interrupt when a START condition is detected. At \_PIP0A the context of the interrupted program is stored. Next Auto-clock generation is disabled and SCL stretching enabled. Reception of the slave address can now begin by calling RCV\_SL\_BY. When the received slave-address is compared with the own-slave-address the R/W-bit is ignored. If there is no match between the 2 addresses, a negative ACK bit is sent and the slave routine is left via EXIT. If there was a match the R/W bit is checked to enter the slave-receiver or slave-transmitter mode.

The slave-transmitter mode starts at NXT\_TRX. After getting the byte from the data buffer via BUF\_POINT and initializing the bit counter BIT\_CNT the transmission loop is entered. A bit is written via access to S1BIT because this will automatically reset the CLH and WBF status flags, and also SCL stretching. Now WBF must be tested until the transmission is successful. When WBF becomes true, SCL will be stretched again. When 8 bits are sent, the SDA line is released and RBF is tested until the ACK bit is received. The ACK bit is read by reading SDI instead of S1BIT to maintain SCL stretching. If ACK was false, no more bytes have to be sent and the routine is left. If another byte has to be transmitted, BUF\_POINT is updated and transmission will continue.

The slave-receiver mode starts at RCV\_SLAVE. A byte is received by calling RCV\_SL\_BY. This routine will clear the CY-flag when a STOP condition has been received. This means that the master will send no more bytes to this slave and the slave routine will be left. When no STOP condition was detected, the received byte will be stored @BUF\_POINT and an ACK bit will be sent. After this, a new byte can be received.

When calling RCV\_SL\_BY the bit counter BIT\_CNT will be initialized and the SCL stretching stopped by a dummy access to S1BIT. In the receive loop both BB and RBF will be checked. When BB is cleared, a STOP condition is detected and the routine will be left with CY=0.

The first 7 bits are received via S1BIT because this will release stretching. The 8th bit is accessed via SDI because stretching must be maintained.

If the slave routine is left via EXIT, the STR bit is cleared (to disable stretching on SCL edges when the 8xC528 is not addressed as slave) and a dummy access to S1BIT is done to finish current SCL stretching. If the slave routine was entered via an interrupt the previous context is restored.

AN438

```

TSW-ASM51 V3.0b Serial #00052252 Slave interrupt routine PAGE 1

```

LOC OBJ LINE SOURCE 1 \$TITLE(Slave interrupt routine) 2 \$DEBUG 3 \$NOLIST 6 ; 7 ;This routine handles I2C interrupts. 8 ;8xC528 I2C interface enters in slave mode. 9 ;After testing R/W bit, 8xC528 will go in slave-transmit or 10 ;slave-receive mode. 11 ;Source or destination buffer for data uses pointer SLAVE\_SUB\_ADDRESS 12 ;Slave routine will use register bank 01 13 ; 14 15 ;Interrupt entry point 16 17 CSEG AT 53H \_\_\_\_ 18 0053: 020000 R 19 LJMP \_\_\_PIPOA ;Vector to interrupt handler 20 ; 21 22 12C\_DRIVER SEGMENT CODE INBLOCK 23 24 RSEG I2C\_DRIVER \_\_\_\_ 25 26 PUBLIC MST\_ENTRY 27 EXTRN DATA(SLAVE\_SUB\_ADDRESS) 28 EXTRN BIT(ARB\_LOST) 29 REG END 30 BUF\_POINT SET RO REG END 31 OWN\_SLAVE SET R7 REG END 32 BIT\_CNT SET R2 33 34 35 0000: COE0 36 \_\_\_PIPOA:PUSH ACC ; Push CPU status on stack R 0002: COD0 37 PUSH PSW 0004: 75D008 38 MOV PSW,#08H ;Select registerbank 01 39 40 41 ;Check slave address 42 43 0007: 43D842 ORL S1SCS,#01000010B ;Disable SCL generation and enable SCL 44 ;stretching stretching 000A: 1142 R 45 ACALL RCV\_SL\_BY ; Receive slave address, on exit SCL is ; stretched ;Store R/W bit in F0 000C: A2E0 46 PROC: MOV C,ACC.0 000E; 92D5 47 MOV F0,C 0010: 6F 48 XRL A,OWN\_SLAVE ;Compare received slave address

AN438

TSW-ASM51 V3.0b Serial #00052252 Slave interrupt routine PAGE 2

| LOC   | OBJ    |   | LINE | SOURCE        |                                     |                                                     |

|-------|--------|---|------|---------------|-------------------------------------|-----------------------------------------------------|

|       |        |   |      |               |                                     |                                                     |

|       |        |   |      |               |                                     |                                                     |

| 0011: | C2E0   |   | 49   |               | CLR ACC.0                           | ;Ignore R/W bit                                     |

| 0013: | 7050   |   | 50   |               | JNZ NO_MATCH                        | ;Leave slave-routine if there is no match           |

| 0015: | C3     |   | 51   |               | CLR C                               | ;Send ACK                                           |

| 0016: | 115C   | R | 52   |               | ACALL SEND_ACK                      |                                                     |

| 0018: | A800   | R | 53   |               | MOV BUF_POINT, SI                   | AVE_SUB_ADDRESS ;Get buffer pointer                 |

| 001A: | A2D5   |   | 54   |               | MOV C,F0                            | ;Restore R/W bit                                    |

| 001C: | 5019   |   | 55   |               | JNC RCV_SLAVE                       | ;Test R/W bit                                       |

|       |        |   | 56   |               |                                     |                                                     |

|       |        |   | 57   |               |                                     |                                                     |

|       |        |   | 58   | ;*****        | * * * * * * * * * * * * * * * * * * | *****************                                   |

|       |        |   | 59   | ;Slave        | transmitter mode                    |                                                     |

|       |        |   | 60   | ;*****        | * * * * * * * * * * * * * * * * * * | ***************                                     |

|       |        |   | 61   |               |                                     |                                                     |

|       |        |   | 62   |               |                                     |                                                     |

| 001E: | Еб     |   | 63   | NXT_TRX       | :MOV A,@BUF_POINT                   | Get byte to send                                    |

| 001F: | 7A08   |   | 64   |               | MOV BIT_CNT,#08                     | ;Init bit counter                                   |

|       |        |   | 65   |               |                                     |                                                     |

| 0021: |        |   | 66   | NXT_TRX       | _BIT:                               |                                                     |

| 0021: | F5D9   |   | 67   |               | MOV S1BIT,A                         | ;Trx bit and stretch after transmission             |

| 0023: | 23     |   | 68   |               | RL A                                | ;Prepare next bit to send                           |

| 0024: | 30DAFD |   | 69   |               | JNB WBF,\$                          | ;Test if bit is sent                                |

| 0027: | DAF8   |   | 70   |               | DJNZ BIT_CNT,NX1                    | TRX_BIT ;Test if all bits are sent                  |

|       |        |   | 71   |               |                                     |                                                     |

| 0029: | D2DF   |   | 72   |               | SETB SDO                            | ;Release SDA line for NO_ACK/ACK reception          |

| 002B: | E5D9   |   | 73   |               | MOV A,S1BIT                         | ;Stop stretching                                    |

| 002D: | 30DBFD |   | 74   |               | JNB RBF,\$                          | ;Test if ACK bit is received                        |

| 0030: | A2DF   |   | 75   |               | MOV C,SDI                           | ;Read bit, SCL remains stretched                    |

| 0032: | 4040   |   | 76   |               | JC EXIT                             | ;NO_ACK received. Exit slave routine                |

| 0034: | 08     |   | 77   |               | INC BUF_POINT                       | -<br>;ACK received. Update pointer for next byte to |

|       |        |   |      |               | _                                   | ; send                                              |

| 0035: | 80E7   |   | 78   |               | SJMP NXT_TRX                        |                                                     |

|       |        |   | 79   |               | —                                   |                                                     |

|       |        |   | 80   | ;*****        | ****                                | *****************                                   |

|       |        |   | 81   | ;Slave        | receiver mode                       |                                                     |

|       |        |   | 82   | ; * * * * * * | ****                                | *****************                                   |

|       |        |   | 83   |               |                                     |                                                     |

| 0037: |        |   | 84   | RCV_SLA       | VE:                                 | ;Entry in slave-receiver mode                       |

| 0037: | 1142   | R | 85   |               | ACALL RCV_SL_BY                     | -                                                   |

| 0039: |        |   | 86   |               | JNC EXIT                            | ; If STOP is detected, then exit                    |

| 003B: |        |   | 87   |               |                                     | A ;Store received byte                              |

| 003C: |        |   | 88   |               | CLR C                               | ;Send ACK                                           |

| 003D: |        | R |      |               | CALL SEND_ACK                       |                                                     |

| 003E: |        |   | 90   |               | INC BUF_POINT                       | ;Update pointer                                     |

| 0040: |        |   | 91   |               | SJMP RCV_SLAVE                      | Receive next byte                                   |

| 00101 |        |   | 92   |               | 2011 100V_011VH                     |                                                     |

|       |        |   | 93   |               |                                     |                                                     |

|       |        |   | 22   |               |                                     |                                                     |

AN438

TSW-ASM51 V3.0b Serial #00052252 Slave interrupt routine PAGE 3

| LOC   | OBJ              | LINE       | SOURCE                                                                                                  |

|-------|------------------|------------|---------------------------------------------------------------------------------------------------------|

|       |                  |            |                                                                                                         |

|       |                  |            |                                                                                                         |

|       |                  | 94         | ;**************************************                                                                 |

|       |                  | 95         | Receive byte routine                                                                                    |

|       |                  | 96         | ;On exit, received byte in accu                                                                         |

|       |                  | 97         | ;On exit CY=0 if STOP is detected<br>;************************************                              |

| 0040. |                  | 98         |                                                                                                         |

| 0042: | 73.00            | 99         | RCV_SL_BY:                                                                                              |

| 0042: |                  | 100        | MOV BIT_CNT,#08                                                                                         |

| 0044. | E5D9             | 101<br>102 | MOV A,S1BIT ;Disable stretching from START or previous ACK<br>CLR A                                     |

| 0040. | 64               | 102        | RCV_BIT:                                                                                                |

|       | 30DC10           | 103        | —                                                                                                       |

|       | 30DEI0<br>30DBFA | 104        | JNB BB,STOP_RCV ;Test if STOP-condition is received<br>JNB RBF,RCV_BIT ;Wait till received bit is valid |

|       | BA0105           | 105        | CJNE BIT_CNT,#01,ASSEM_BIT ;Check if last bit is to be received                                         |

| 004D. | BAULUS           | 100        | COME BII_CMI, #01, ASSEM_BII / CHECK II TASE DIE IS EO DE TECEIVED                                      |

| 0050: | 7 2 D F          | 108        | MOV C,SDI ;Get last bit without stopping stretching                                                     |

| 0052: |                  | 109        | RLC A                                                                                                   |

| 0053: |                  | 110        | SETB C ;No STOP detected                                                                                |

| 0054: |                  | 111        | RET                                                                                                     |

| 0051  | 22               | 112        |                                                                                                         |

| 0055: |                  | 113        | ASSEM_BIT:                                                                                              |

| 0055: |                  | 114        | ORL A,S1BIT ;Receive bit; release RBF,CLH and SCL stretching                                            |

| 0057: |                  | 115        | RL A                                                                                                    |

| 0058: |                  | 116        | DJNZ BIT_CNT, RCV_BIT                                                                                   |

|       |                  | 117        |                                                                                                         |

| 005A: |                  | 118        | STOP_RCV:                                                                                               |

| 005A: | C3               | 119        | CLR C ;STOP detected                                                                                    |

| 005B: | 22               | 120        | RET                                                                                                     |

|       |                  | 121        |                                                                                                         |

|       |                  | 122        | ;**************************************                                                                 |

|       |                  | 123        | ;Send ACK/NO_ACK. Value of ACK in Carry                                                                 |

|       |                  | 124        | ;**************************************                                                                 |

| 005C: |                  | 125        | SEND_ACK:                                                                                               |

| 005C: | 13               | 126        | RRC A                                                                                                   |

| 005D: | F5D9             | 127        | MOV S1BIT,A ;Carry to SDA line                                                                          |

| 005F: | 30DAFD           | 128        | JNB WBF,\$ ;Test if ACK/NO_ACK is sent                                                                  |

| 0062: | D3DF             | 129        | SETB SDO ;Release SDA line                                                                              |

| 0064: | 22               | 130        | RET                                                                                                     |

|       |                  | 131        |                                                                                                         |

|       |                  | 132        | ;**************************************                                                                 |

|       |                  | 133        | ;No match between received slave-address and own-slave-address                                          |

|       |                  | 134        | ;**************************************                                                                 |

| 0065: |                  | 135        | NO_MATCH:                                                                                               |

| 0065: | D3               | 136        | SETB C ; Send NO_ACK                                                                                    |

| 0066: | 115C R           | 137        | ACALL SEND_ACK                                                                                          |

| 0068: | 800A             | 138        | SJMP EXIT                                                                                               |

|       |                  |            |                                                                                                         |

AN438

| TSW-AS | M51 | V3.0b | Serial | #00052252 | Slave | interrupt | routine |

|--------|-----|-------|--------|-----------|-------|-----------|---------|

| PAGE   | 4   |       |        |           |       |           |         |

| LOC O   | )BJ   | LINE  | SOURCE  |                                     |                                                               |

|---------|-------|-------|---------|-------------------------------------|---------------------------------------------------------------|

|         |       |       |         |                                     |                                                               |

|         |       | 139   |         |                                     | * * * * * * * * * * * * * * * * * * * *                       |

|         |       | 141   | ;Entry  | point when an a                     | rbitration-lost condition is detected in                      |

|         |       |       | ;master |                                     |                                                               |

|         |       | 142   | 2 ;**** | * * * * * * * * * * * * * * * * * * | * * * * * * * * * * * * * * * * * * * *                       |

| 006A:   |       | 143   | MST_ENT | TRY:                                |                                                               |

| 006A: 2 | 23    | 144   |         | RL A                                | Restore slave address sofar                                   |

| 006B: C | C2E0  | 145   |         | CLR ACC.0                           |                                                               |

| 006D: 4 | 3D842 | 146   |         | ORL SISCS,#0100                     | 00010B ;Disable SCL generation and enable SCL<br>;strectching |

| 0070: 1 | 147   | R 147 |         | ACALL RCV_BIT                       | ;Proceed with receiving rest of slave address                 |

| 0072: 8 | 8098  | 148   |         | SJMP PROC                           |                                                               |

|         |       | 149   |         |                                     |                                                               |

|         |       | 150   |         |                                     |                                                               |

|         |       | 153   | ;****   | * * * * * * * * * * * * * * * * *   | ****************                                              |

|         |       | 152   | ;Exit i | from interrupt ro                   | outine                                                        |

|         |       | 153   | 3 ;**** | * * * * * * * * * * * * * * * * *   | *****************                                             |

|         |       | 154   |         |                                     |                                                               |

| 0074: C | 2D9   | 155   | EXIT:   | CLR STR                             | ;Disable stretching on next falling SCL edges                 |

| 0076: E | 5D9   | 156   |         | MOV A,S1BIT                         | ;Stop current SCL stretching                                  |

| 0078: 3 | 80001 | R 157 |         | JNB ARB_LOST, EX                    | K_SL                                                          |

| 007B: 2 | 22    | 158   |         | RET                                 | ;Exit when entered from master mode                           |

| 007C: D | 0D0   | 159   | EX_SL:  | POP PSW                             | ;Restore old CPU status                                       |

| 007E: D | 0E0   | 160   |         | POP ACC                             |                                                               |

| 0080: 3 | 32    | 161   |         | RETI                                |                                                               |

|         |       | 162   |         |                                     |                                                               |

| 0081:   |       | 163   |         | END                                 |                                                               |

|         |       |       |         |                                     |                                                               |

### 4.0 EXAMPLES

### 4.1 Introduction

Some examples are given how to use the I<sup>2</sup>C routines in an application program. Examples are given for assembly, PL/M and C program.

The program displays time from the PCF8583P clock/calendar/RAM on an LCD display driven by the PCF8577.

The example can be executed on the OM4151  $I^2C$  evaluation board.

### 4.2 Using the Routines with Assembly Sources

The listing of the example program is shown on page 17. The most important aspect when using the  $I^2C$  routines is preparing the input parameters before the sub-routine call. When, for example, the IIC\_Write routine must be called, the parameters must be called in the following order:

MOV\_IIC\_READ\_BYTE,#SLAVE\_ADR MOV\_IIC\_READ\_BYTE+1,#COUNT\_1 MOV\_IIC\_READ\_BYTE+2,#SOURCE\_PTR\_1 CALL\_IIC\_READ

Note that the order of defining the parameters is the same as in a PL/M-call. An easier way to call the routines is making a macro that includes the initializing of the parameters. The example program makes use of macros.

IIC\_Read is then called in the following way:

%IIC\_Read(Slave\_Adr,Count\_1,Source\_Ptr\_1);

Note that in the listing the contents of the macro are shown, instead of the call.

The macro must be written as follows:

%\* DEFINE (IIC\_Read(SLAVE\_ADR,COUNT\_1,SOURCE\_PTR\_1)) (MOV\_IIC\_READ\_BYTE,#%SLAVE\_ADR MOV\_IIC\_READ\_BYTE+1,#%COUNT\_1 MOV\_IIC\_READ\_BYTE+2,#%SOURCE\_PTR\_1 LCALL\_IIC\_READ)

Macros for the I<sup>2</sup>C CALLs are found in I2C.MAC. This file should be included in all modules making use of the macros. One of the modules should also include the variable definitions needed by the I<sup>2</sup>C routines. These are found in file VAR\_DEF.ASM. If the program consists of more than 1 module, then these modules should also include EXT\_VAR.ASM. This file contains the EXTRN- definitions of the I<sup>2</sup>C routines.

When and  $l^2C$  routine is called, the accumulator contains status information and the CY-bit is set if an error has occurred. The contents of the accumulator are the same as the returned byte when using PL/M.

Application note

# AN438

| TSW-ASM        | M51 V3.0   | b Seri | l #00052252 Assembly example program      | PAGE 1                         |

|----------------|------------|--------|-------------------------------------------|--------------------------------|

| LOC (          | OBJ        | LIN    | SOURCE                                    |                                |

|                |            |        | \$TITLE(Assembly example program)         |                                |

|                |            |        | \$DEBUG                                   |                                |

|                |            |        |                                           |                                |

|                |            |        | Hours and minutes will be displayed or    |                                |

|                |            |        | ; ;Dot between hours and minutes will bli | .nk                            |

|                |            |        | ,<br>7 \$                                 | ;Include I2C var. definitions  |

|                |            |        | <pre>3 # 1 "C:\USER\VAR_DEF.ASM"</pre>    | finerade ize var. dermittons   |

|                |            |        | # 8 "DEMO_ASM.ASM"                        |                                |

|                |            |        | \$                                        | ;Include I2C macro's           |

|                |            |        | # 1 "C:\USER\I2C.MAC"                     |                                |

|                |            | 3      | # 9 "DEMO_ASM.ASM"                        |                                |

| 00A2           |            | 1      | CLOCK_ADR EQU 0A2h                        | ;Address of PCF8583            |

| 0001           |            | 1      | . CL_SUB_ADR EQU 01h                      | ;Sub address for reading time  |

| 0074           |            | 1      | LCD_ADR EQU 74h                           | ;Address of PCF8577            |

|                |            | 1      |                                           |                                |

|                |            | 1      | RAMVAR SEGMENT DATA                       | ;Segment for variables         |

|                |            | 1      | USER SEGMENT DATA                         | ;Segment for application       |

|                |            |        |                                           | ;program                       |

|                |            | 1      |                                           |                                |

|                |            | 1      |                                           |                                |

| :0000          |            | R 1    |                                           | ;Stack area                    |

| 000A:<br>000E: |            | 1      | -                                         | ;Buffer for I2C strings        |

| 0006.          |            | 2      | —                                         |                                |

|                |            | 2      |                                           |                                |

| 0000: (        | 020000     | R 2    |                                           |                                |

|                |            | 2      | —                                         |                                |

|                |            | 2      |                                           |                                |

|                |            | 2      | RSEG USER                                 |                                |

|                |            | 2      | ,                                         |                                |

| 0000:          |            | R 2    | APL_START:                                |                                |

| 0000: 9        | 900073     | R 2    | MOV DPTR, #LCD_TAB                        | ;Pointer to segment table      |

| 0003: 7        | 7581FF     | R 3    | MOV SP,#STACK-1                           | ;Initialize stack              |

| 0006: 7        | 750E00     | R 3    |                                           | ;Control word for LCD driver   |

|                |            | 3      |                                           |                                |

| 0009: '        |            | R 3    |                                           |                                |

| 000C: '        |            | R 3    |                                           |                                |

| 000F: 1        | 120000     | R 3    |                                           |                                |

| 0012: 1        | с <i>1</i> | 3      |                                           | ;Prepare buffer for clock int. |

| 0012: 1        |            | R 3    |                                           | TECHNE DATIET FOT CIUCK IIIC.  |

| 0015: 1        |            | R 3    | — ·                                       |                                |

|                |            | 4      |                                           |                                |

| 0017: 7        | 7500A2     | R 4    |                                           |                                |

| 001A: '        |            | R 4    |                                           |                                |

| 001D: '        | 75020A     | R 4    | MOV _IIC_Write_Byte+2,#TIME_BUFFER        |                                |

| 0020: 2        | 120000     | R 4    | LCALL _IIC_Write                          |                                |

|                |            |        |                                           |                                |

# AN438

| TSW-A | SM51 V3.0 | b Se | erial    | #00052252 Assembly example program       | PAGE 2                       |

|-------|-----------|------|----------|------------------------------------------|------------------------------|

| LOC   | OBJ       | I    | LINE     | SOURCE                                   |                              |

|       |           |      | 45<br>46 | ;Initialize clock                        |                              |

| 0023: |           |      | 47       | REPEAT:                                  |                              |

| 0023: | 7500A2    | R    | 48       | MOV _IIC_Read_Sub_Byte ,#CLOCK_ADR       |                              |

|       | 750104    | R    | 49       | MOV _IIC_Read_Sub_Byte+1,#4              |                              |

|       | 75020A    | R    | 50       | MOV _IIC_Read_Sub_Byte+2,#TIME_BUFFE     | R                            |

| 002C: | 750301    | R    | 51       | MOV _IIC_Read_Sub_Byte+3,#CL_SUB_ADR     |                              |

|       | 120000    | R    | 52       | LCALL _IIC_Read_Sub                      |                              |

|       |           |      | 53       | Read time                                |                              |

|       |           |      | 54       |                                          |                              |

|       |           |      | 55       | ;Time has been read. Order: hundreds of  | sec's, sec's, min's and hr's |

| 0032: | E50D      | R    | 56       |                                          | ;Mask of hour counter        |

| 0034: | 543F      |      | 57       | ANL A,#3Fh                               |                              |

|       | F50D      | R    | 58       | MOV TIME_BUFFER+3,A                      |                              |

|       |           |      | 59       |                                          |                              |

| 0038: | 120054    | R    | 60       | CALL CONVERT                             | ;Convert time data to LCD    |

|       |           |      |          |                                          | ;segment data                |

|       |           |      | 61       |                                          |                              |

|       |           |      | 62       | ;Check if dot has to be switched on      |                              |

| 003B: | 431101    | R    | 63       | ORL LCD_BUFFER+3,#01h                    |                              |

|       |           |      | 64       | ;If lsb of seconds is '0', then switch o | n dp                         |

| 003E: | E50B      | R    | 65       | MOV A, TIME_BUFFER+1                     | ;Get seconds                 |

| 0040: | 13        |      | 66       | RRC A                                    |                              |

| 0041: | 4003      |      | 67       | JC PROCEED                               |                              |

| 0043: | 430F01    | R    | 68       | ORL LCD_BUFFER+1,#01                     | ;Switch on dp                |

|       |           |      | 69       |                                          |                              |

|       |           |      | 70       | ;Display new time                        |                              |

| 0046: |           |      | 71       | PROCEED:                                 |                              |

| 0046: | 750074    | R    | 72       | MOV _IIC_Write_Byte ,#LCD_ADR            |                              |

| 0049: | 750105    | R    | 73       | MOV _IIC_Write_Byte+1,#5                 |                              |

| 004C: | 75020E    | R    | 74       | MOV _IIC_Write_Byte+2,#LCD_BUFFER        |                              |

| 004F: | 120000    | R    | 75       | LCALL _IIC_Write                         |                              |

|       |           |      | 76       |                                          |                              |

| 0052: | 80CF      |      | 77       | SJMP REPEAT                              | ;Read new time               |

|       |           |      | 78       |                                          |                              |

|       |           |      | 79       |                                          |                              |

|       |           |      | 80       | ;CONVERT converts BCD data of time to se | gment data                   |

| 0054: | 780F      | R    | 81       | CONVERT:MOV R0,#LCD_BUFFER+1             | ;R0 is pointer               |

| 0056: | E50D      | R    | 82       | MOV A, TIME_BUFFER+3                     | ;Get hours                   |

| 0058: | C4        |      | 83       | SWAP A                                   | ;Swap nibbles                |

|       | 12006D    | R    | 84       | CALL LCD_DATA                            | ;Convert 10's of hours       |

|       | E50D      | R    | 85       | MOV A, TIME_BUFFER+3                     |                              |

|       | 12006D    | R    | 86       | CALL LCD_DATA                            | ;Convert hours               |

|       | E50C      | R    | 87       | MOV A, TIME_BUFFER+2                     | ;Get minutes                 |

| 0063: |           |      | 88       | SWAP A                                   |                              |

|       | 12006D    | R    | 89       | CALL LCD_DATA                            | ;Convert 10's of minutes     |

|       | E50C      | R    | 90       | MOV A, TIME_BUFFER+2                     |                              |

| 0069: | 12006D    | R    | 91       | CALL LCD_DATA                            | ;Convert minutes             |

## AN438

| TSW-ASM51 V3.0b | Serial | #00052252 Assembly example program   | PAGE 3                          |

|-----------------|--------|--------------------------------------|---------------------------------|

| LOC OBJ         | LINE   | SOURCE                               |                                 |

| 006C: 22        | 92     | RET                                  |                                 |

|                 | 93     |                                      |                                 |

|                 | 94     | ;LCD_DATA gets data from segment tab | ole and stores it in LCD_BUFFER |

| 006D:           | 95     | LCD_DATA:                            |                                 |

| 006D: 540F      | 96     | ANL A,#OFH                           | ;Mask off LS-nibble             |

| 006F: 93        | 97     | MOVC A, @A+DPTR                      | ;Get segment data               |

| 0070: F6        | 98     | MOV @R0,A                            | ;Save segment data              |

| 0071: 08        | 99     | INC RO                               |                                 |

| 0072: 22        | 100    | RET                                  |                                 |

|                 | 101    | ;                                    |                                 |

|                 | 102    | ;Conversion table for LCD            |                                 |

| 0073:           | 103    | LCD_TAB:                             |                                 |

| 0073: FC60DA    | 104    | DB 0FCH,60H,0DAH                     | ;'0','1','2'                    |

| 0076: F266B6    | 105    | DB 0F2H,66H,0B6H                     | ;'3','4','5'                    |

| 0079: 3EE0FE    | 106    | DB 3EH, OEOH, OFEH                   | ;'6','7','8'                    |

| 007C: E6        | 107    | DB 0E6H                              | ; ' 9 '                         |

|                 | 108    | ;                                    |                                 |

| 007D:           | 109    | END                                  |                                 |

#### 4.3 Using the Routines with PL/M-51 Sources

The following listing shows the listing of the clock program in PL/M-51. The procedures are untyped. The routines are used the same way as in the examples of chapter 3.2.

\$OPTIMIZE(4) \$DEBUG \$CODE

/\* Hours and minutes will be displayed on LCD display

Dots between hours and minutes will blink \*/

```

Demo_plm: Do;

```

```

/* External declarations */

```

```

Init_IIC: Procedure(Own_Adr,Slave_Ptr) External;

Declare (Own_Adr,Slave_Ptr) Byte Main;

```

```

End Init_IIC;

```

```

AN438

```

```

Clock: Do;

/* Variable and constant declarations */

Declare LCD_TAB(*) Byte Constant (0FCh,60H,0DAH,0F2H,66H,

OB6H, 3EH, OEOH, OFEH, OE6H);

Declare Time_Buffer(4) Byte Main;

Declare LCD_Buffer(5) Byte Main;

Declare Tab_Point Word Main;

Declare (LCD_Point, Time_Point) Byte Main;

Declare Segment Based LCD_Point Byte Main;

Declare Time Based Time_Point Byte Main;

Declare Tab_Value Based Tab_Point Byte Constant;

Declare clock_Adr Literally '0A2h';

Declare LCD_Adr Literally '74h';

Declare C1_Sub_Adr Literally '01h';

Call Init_IIC(22h,.Time_Buffer);

LCD_Buffer(0)=0; /* LCD control word */

Time_Buffer(0)=0;

Time_Buffer(1)=0;

Call IIC_Write(Clock_Adr,2,.Time_Buffer); /* Initialize clock */

Do While LCD_Buffer(0)=0; /* Program loop */

Call IIC_Read_Sub(Clock_Adr, 4,.Time_Buffer, Cl_Sub_Adr);

/* Get time */

LCD_Point=.LCD_Buffer+1; /* Initialize pointers */

Time_point=.Time_Buffer(3);

Tab_Point=.LCD_Tab(0)+SHR(Time,4); /* 10-HR's */

Segment=Tab_Value;

LCD_Point=LCD_Point+1;

Tab_Point=.LCD_Tab(0)+(Time AND 0FH); /* HR's */

Segment=Tab_Value;

Time_Point=Time_Point-1;

LCD_Point=LCD_Point+1;

Tab_Point=.LCD_Tab+SHR(Time,4); /* 10-MIN's */

Segment=(Tab_Value OR 01H); /* dp */

LCD_Point=LCD_Point+1;

Tab_Point=.LCD_Tab+(Time AND 0FH); /* MIN's */

Segment=Tab_Value;

Time_Point=.Time_Buffer(1)+1; /*Check sec's for blinking */

LCD_Point=.LCD_Buffer+1;

If (Time AND 01H)>0 then Segment=(Segment OR 01H);

Call IIC_Write(LCD_Adr,5,.LCD_Buffer); /* Display time */

End;

```

End Clock;

End Demo\_plm;

### AN438

### 4.4 Using the Routines with C Sources

An example of a C program using the I<sup>2</sup>C routines follows. Function prototypes are found in header file "i2c.h". In this example the function prototypes are written in such a way that not value is returned by the function. If the STATUS byte is needed, the header file may be changed to return a byte. Note that the function calls are written in upper-case. This is due to the fact that the used version of the assembler/linker is case sensitive.

```

#include <C:\USER\i2c.h>

```

```

rom char

```

LCD\_Tab[]={0xFC,0x60,0xDA,0xF2,0x66,0x86,0x3E, 0xE0,0xFE,0xE6};

void main()

```

{

```

```

#define Clock Adr

0xA2

#define LCD_Adr

0x74

#define C1_Sub_Adr

0 \times 01

* Tab_Ptr;

rom char

data char

Time_Buffer[4];

data char

* Time_Ptr;

LCD_Buffer[5];

data char

data char

* LCD_Ptr;

INIT_IIC(0x22,&Time_Buffer);

LCD_Buffer[0]=0; /* LCD control word */

Time_Buffer[0]=0;

Time_Buffer[1]=0;

IIC_WRITE(Clock_Adr,2,&Time_Buffer); /* Initialize clock */

while (1)

/* Program loop */

{

IIC_READ_SUB(Clock_Adr,4,&Time_Buffer,C1_Sub_Adr);

/* Get time */

LCD_Ptr = &LCD_Buffer[1]; /* Initialize pointers */

Time_Ptr = &Time_Buffer[3];

Tab_Ptr = (LCD_Tab+(*Time_Ptr >> 4)); /* 10-HR's */

*(LCD_Ptr++) = *Tab_Ptr;

Tab_Ptr = (LCD_Tab+(*(Time_Ptr--) & 0x0F)); /* HR's */

*(LCD_Ptr++) = *Tab_Ptr;

Tab_Ptr = (LCD_Tab+(*Time_Ptr >> 4)); /* 10-MIN's */

*(LCD_Ptr++) = (*Tab_Ptr | 0x01); /* dp */

Tab_Ptr = (LCD_Tab+(*Time_Ptr & 0x0F)); /* MIN's */

*LCD_Ptr = *Tab_Ptr;

Time_Ptr = &Time_Buffer[1]; /* Check sec's for blinking */

LCD_Ptr = &LCD_Buffer[1];

if ((*Time_Ptr & 0x01)>0)

*LCD_Ptr = (*LCD_Ptr | 0x01);

IIC_WRITE(LCD_Adr,5,&LCD_Buffer); /* Display time */

}

```

}

## AN438

### 5.0 CONTENTS OF DISK

#### A disk contains the following 3 directories:

1: \USER

| This director contains the files that may be used in the user program. |                                                                      |  |

|------------------------------------------------------------------------|----------------------------------------------------------------------|--|